The PC I Base Addresses (BADDR) are automatically assigned by the host at boot time, with the requested resources as outlined in the following table:

| Common Resources & Mapping | ||||||

| PCI BADDRn | Range (Bytes) | Resource | Host BADDRn+Offset (Byte Boundary) | DSP External CEn | DSP Base Address (Byte Boundary) | |

| n/a | 64K-2M | Add-on Init Buffer (DSP Side Only) | n/a | 0 | 0x8000,0000~0x801F,FFFF | |

| 0 | 256 | PLX OpRegs | Memory Mapped | 0x00~0xFF | 0x8034,0000~0x8034,00FF | |

| 1 | I/O Mapped (unused) | |||||

| 2 | 8M | FPGA: 2x 32 Deep FIFO | 0x00,0000~0x0F,FFFF | 0x8020,0000~0x802F,FFFF | ||

| FPGA: x64 Comm Regs | 0x10,0000~0x13,FFFF | 0x8030,0000~0x8033,FFFF | ||||

| FPGA: x12 CSRs | CSR11: 0x10,0100~0x10,40FF | 0x8030,0100~0x8030,40FF | ||||

| CSR[0:10]: 0x14,0000~0x1B,FFFF | 0x803C,0000~0x803C,FFFF | |||||

| Expansion Module (64Kx32) | 0x1C,0000~0x1F,FFFF | 0x8038,0000~0x803B,FFFF | ||||

| BootMEM (SRAM=512kx8SRAM/NOR=1Mx16) | 0x20,0000~0x7F,FFFF | 1 | 0x9000,0000~0x9FFF,FFFF | |||

| 3 | 128K | n/a | n/a | n/a | n/a | |

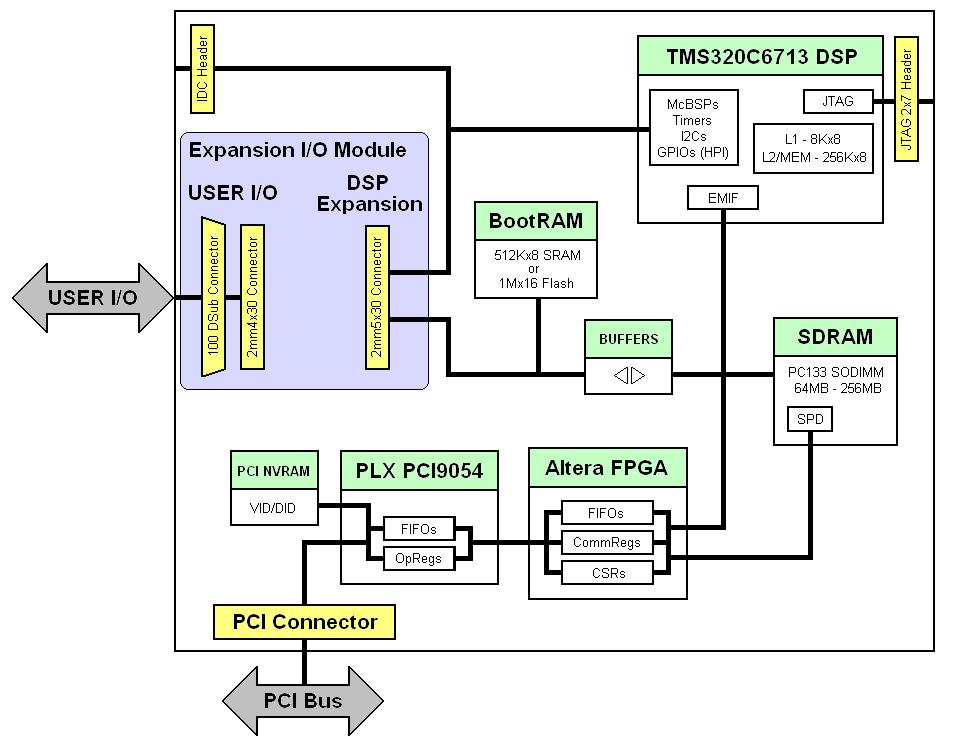

The DSP's resource access is split between onchip SRAM along with the external memory interface (EMIF). The EMIF is partitioned into four separate pages, with varying depths per page. Each page is externally identified in hardware with the CE[3:0] signals. Please consult the C6x's documentation for more details:

| DSP Mapping | ||||

| DSP Space | Resource | Used Physical Range (DWord) | DSP Base Address (Byte Boundary) | |

| Onchip | Internal SRAM | L2: 192k | 0x0000,0000-0x0002,FFFF | |

| Cache: 64k | 0x0003,0000-0x0003,FFFF | |||

| External CEn | 0 | Add-on Init Buffer (DSP Only) | 16K-512K | 0x8000,0000-0x801F,FFFF |

| FPGA: 2x32 FIFO | 1 | 0x8020,0000 | ||

| FPGA: CommRegs | 64 | 0x8030,0000-0x8030,00FF | ||

| PLX Registers | 64 | 0x8034,0000-0x8034,00FF | ||

| Expansion Module | 64k | 0x8038,0000-0x803B,FFFF | ||

| FPGA: CSRs | 5 | CSR11: 0x8030,0100-0x8030,0103 | ||

| CSR[0, 3, 8, 9]: 0x803C,0000-0x803C,C000 | ||||

| 1 | BootMEM | SRAM: 512Kx8 | 0x9000,0000-0x9FFF,FFFF | |

| NOR Flash: 1Mx16 (Optional) | ||||

| 2 | SDRAM | 32MB~128MB | 0xA000,0000-0xAFFF,FFFF | |

| 3 | 32MB~128MB (Optional) | 0xB000,0000-0xBFFF,FFFF | ||